1. 打开Vivado 2018.3 GUI或者打开Vivado 2018.3 tcl command prompt,在tcl命令行的部分输入命令打开vcu_audio_proj.tcl文件的存放目录文件夹;

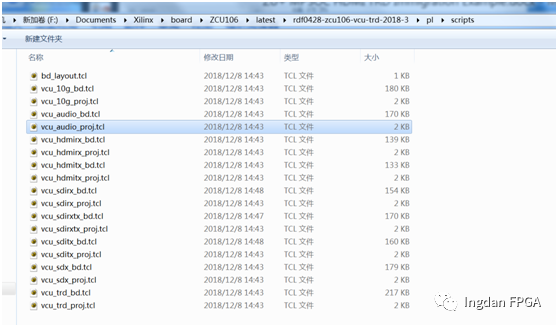

ZCU106 TRD文件目录

2. source vcu_audio_proj.tcl,创建工程,此时vcu_audio_proj.tcl会调用vcu_audio_bd.tcl;

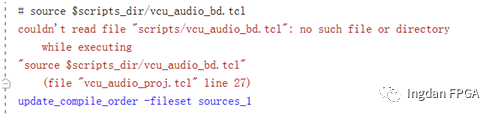

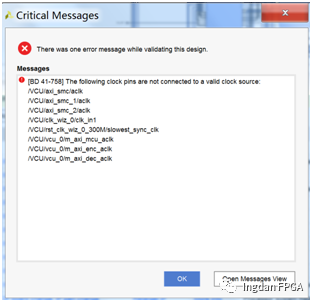

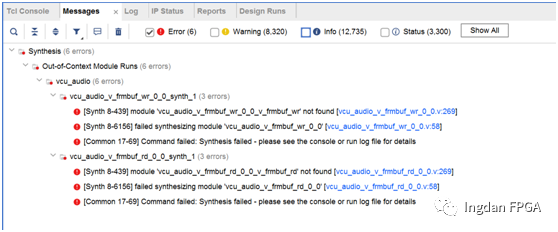

3. 然后我们在打印信息中可以看到如下错误,原因是vcu_audio_proj.tcl中的路径定义问题;

TRD tcl脚本执行错误信息

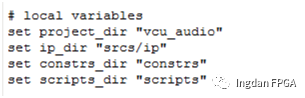

路径定义命令

4. 解决办法为把vcu_audio_proj.tcl和vcu_audio_bd.tcl拷贝到向上一级目录,让vcu_audio_proj.tcl中的路径定义生效即可;拷贝后的路径如下:

拷贝脚本后目录

5. 使用Vivado 2018.3 GUI或者Vivado 2018.3 tcl command prompt打开新的vcu_audio_proj.tcl路径位置,source vcu_audio_proj.tcl创建工程;

6. 此时建议备份ZCU106的TRD工程,下一步有用;

接下来我们把设计移植到用户自己设计的硬件板卡,我的操作步骤如下:

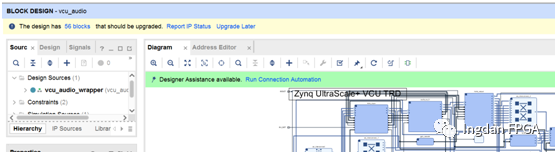

1. 在工程设置中把Project Device从ZCU106修改为客户的PN,我的设计中使用的是XCZU4EV-1FBVB900I;然后Vivado会提示需要Upgrade IP;

upgrade IP

2. 点击Report IP Status,upgrade所有IP;

3. Upgrade IP之后会出现连线报错,是因为Vivado upgrade IP的时候VCU block里面的时钟没有upgrade正确,请参考ZCU106 TRD工程把VCU里面的clk_wiz_0配置为差分输入、不要reset端口、两路输出时钟、clk_out2连接好,并且连接在block design中丢失的信号连接;

信号连接丢失

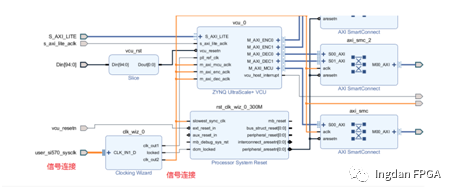

需要修改的block design信号连接

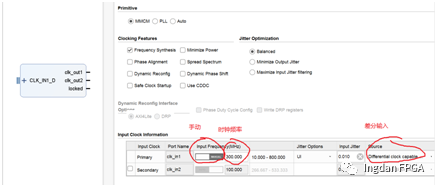

需要修改的clk_wiz输入时钟配置

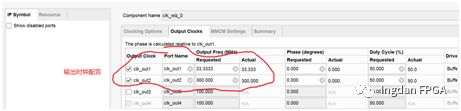

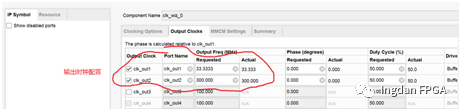

需要修改的clk_wiz输出时钟配置

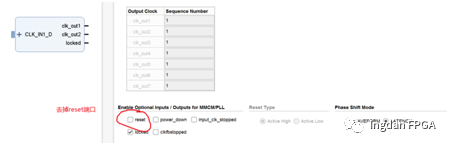

需要修改的reset端口

4. 然后我们去执行Block Design的Validate,可以通过,但是在综合之前产生block design的输出文件时会遇到frame_buffer的错误如下,这个错误是因为工程路径超过了260个字符,需要把工程拷贝到某个盘符的根目录下;

frame buffer错误信息

5. 这时候整个设计可以综合完,我们需要根据用户的硬件原理图设计修改管脚位置约束、电平标准约束等信息;如果所有约束都修改完后编译遇到GTH的参考时钟无法布线成功,是因为block design中vid_phy_controller中参考时钟的位置和用户在硬件上的管脚、器件自身的位置关系等不一致;

[DRC RTSTAT-1] Unrouted nets: 3 net(s) are unrouted. The problembus(es) and/or net(s) are vcu_audio_i/gt_refclk_buf/ibufds_gt/U0/IBUF_OUT[0],vcu_audio_i/vid_phy_controller/inst/gt_usrclk_source_inst/gtrefclk0_in[0], and vcu_audio_i/vid_phy_controller/inst/gt_usrclk_source_inst/gtrefclk1_in[0].

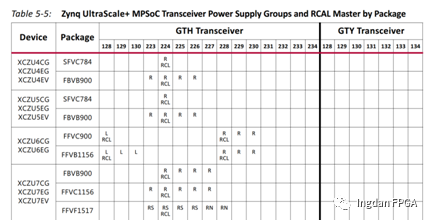

以ZU4EV-FBVB900封装为例,结合用户的原理图设计、ZU+ MPSOC EV系列的GTH位置关系,决定了block design中的连线和vid_phy_controller中的配置:

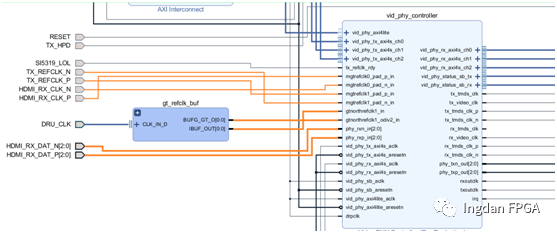

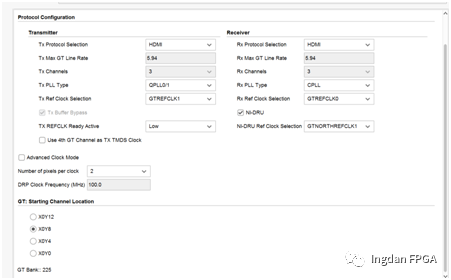

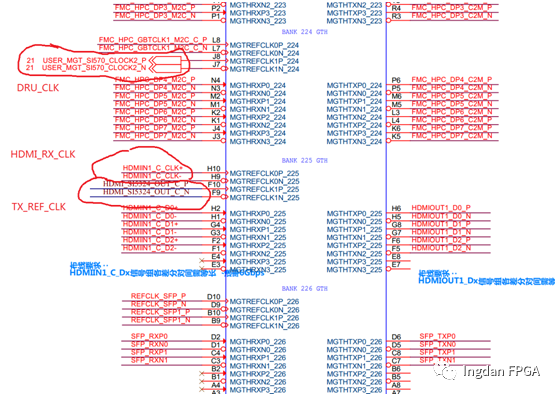

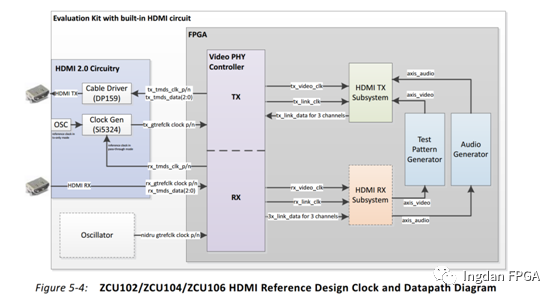

在用户的原理图中,TX_REFCLK_P/N和HDMI_RX_CLK_P/N和HDMI的数据线都是放在GTH BANK225,TX_REFCLK_P/N接BANK225的REFCLK1,HDMI_RX_CLK_P/N接BANK225的REFCLK0,因此在vid_phy_controller的配置中我们要选择GT Starting Channel Location中要选择X0Y8,TX Ref Clock Selection选择GTREFCLK1,RX Ref Clock Selection选择GTREFCLK0;

在用户的原理图中,DRU_CLK_P/N从GTH BANK224的MGTREFCLK1进入,根据ZU4EV-FBVB900封装的GTH位置关系,BANK224处于BANK225的North位置,所以在vid_phy_controller的配置中NI-DRU Ref Clock Selection选择GTNORTHREFCLK1;

block design中的信号连接关系

video_phy_controller中的配置信息

ZU+MPSOC EV GTH Location

用户原理图设计

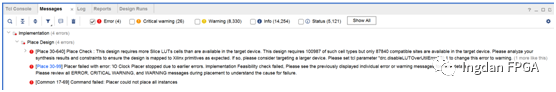

6. 但是在MAP阶段会遇到如下错误,原因是这个设计使用的LUT超出了ZU4EV芯片的总量;可以使用 set_param drc.disableLUTOverUtilError 1命令让设计向下编译,如果不用audio部分,也可以删除掉block design里面的audio部分;删除audio部分之后这个设计在ZU4EV是可以放下的;

MAP错误信息

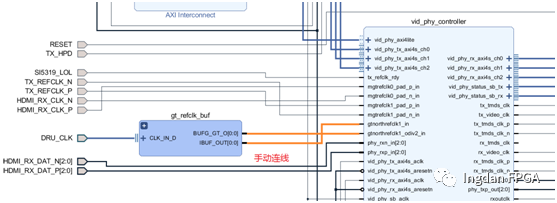

7. 若上一步使用删除block design中的audio部分,block design中还有有一些信号线连接丢失,需要自己手动连接;

删除audio模块后手动连线

删除audio模块后手动连线

8. 此时编译又遇到了URAM占用量超过ZU4EV器件总量的报错,原因是TRD设计中VCU的默认配置为encoder和decoder都是4Kx60fps分辨率,且encoder buffer全部使用URAM实现,ZU4EV没有这么多的URAM,可以修改URAM的资源实现方式来编译通过;也可以减小分辨率以减少URAM占用;

VCU配置信息

HDMI时钟结构图

Ingdan FPGA微信公众号,是科通知识分享平台,欢迎关注。

Ingdan FPGA微信公众号,是科通知识分享平台,欢迎关注。