在一些工业应用中不管出于成本还是功耗又或者集成难度可能不需要DDR,这些系统只需要很小的内存空间来存储和执行其应用程序,对于这些系统OCM可以满足其与存储器相关的需求。用户只需要从OCM执行引导程序和应用程序。如果OCM大小也不足以存储和执行应用程序,用户也可以从QSPI Flash来执行应用程序代码,但是从flash中获取指令会比从OCM中执行要慢,那本文主要介绍在OCM空间不足时从flash执行应用程序时如何提高性能。

在Xilinx官方也是有这部分的详细介绍,详情可以参考如下链接:

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842377/Zynq-7000+AP+SoC+Boot+-+Booting+and+Running+Without+External+Memory+Tech+Ti

1.参考设计主要包含以下几点:

FSBL XIP 模式execution。

提供示例例程以在 FSBL 中将数据/代码预加载到 L2 缓存。

显示 Zynq-7000 SOC 中的 L2 缓存锁定功能。

PL 中 AXI 定时器的参考设计。

显示中断工作概念。

C 和 C++ 应用程序在 L2 缓存锁定模式下运行。

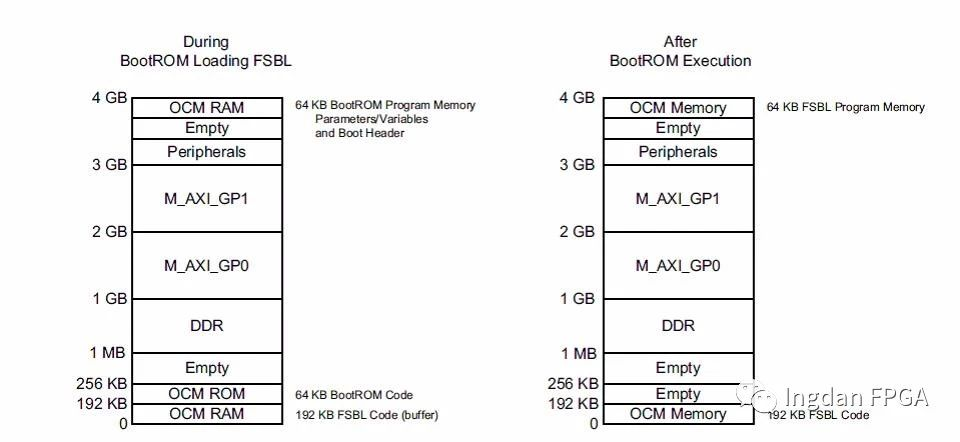

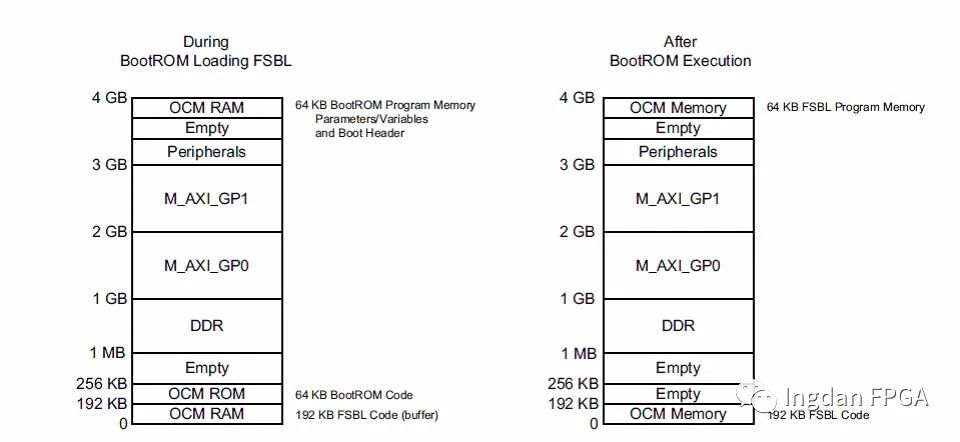

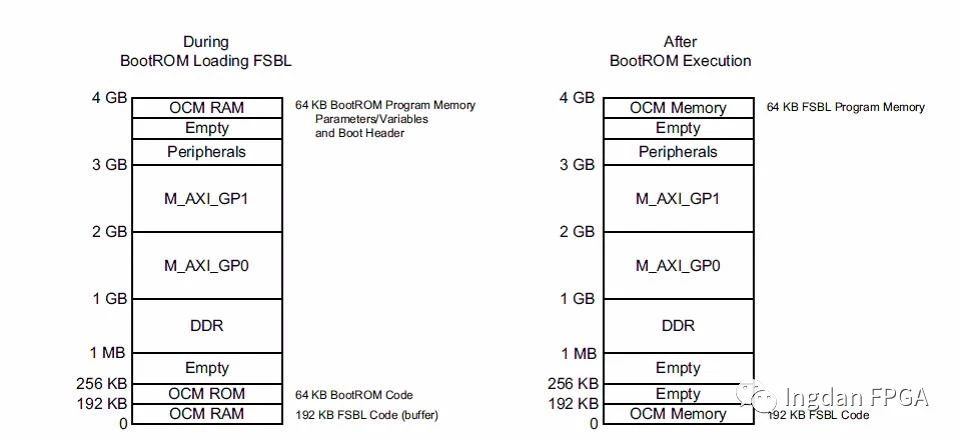

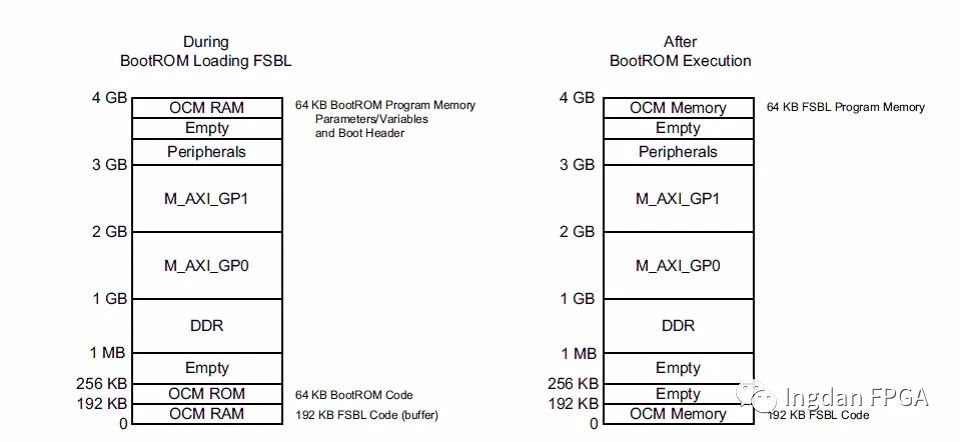

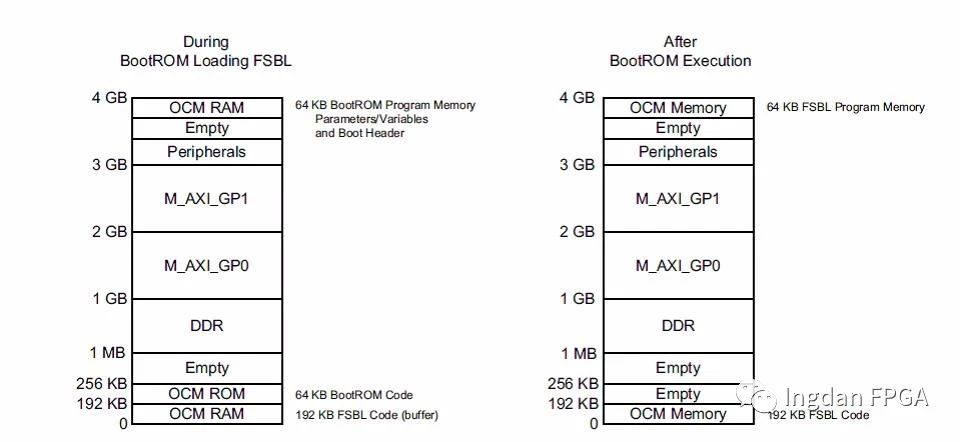

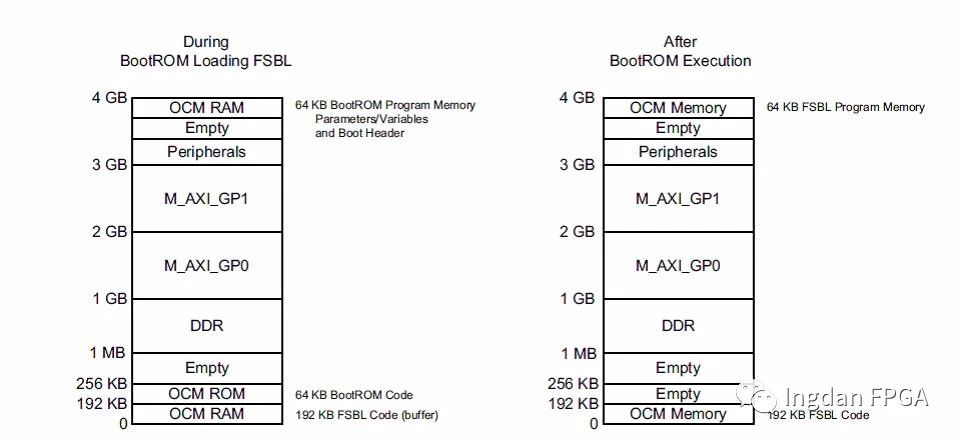

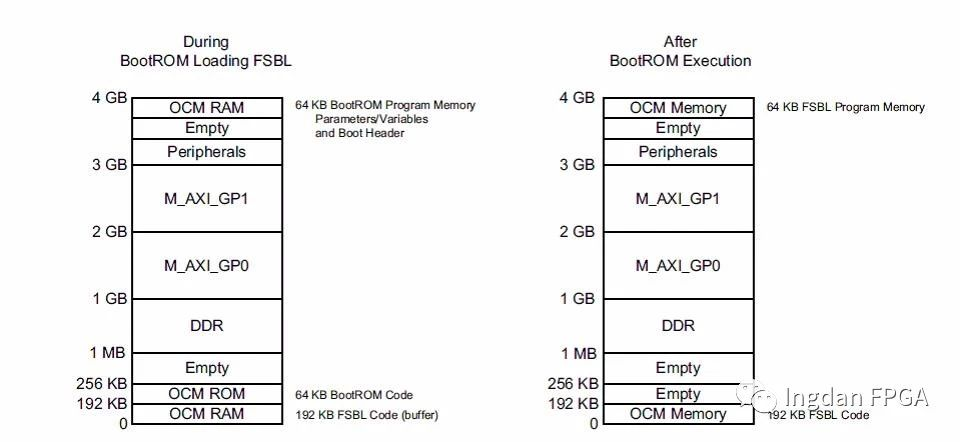

2.OCM Memory Map

3.主要修改的部分

Main.c - Disable DDR checking

Xil_exception.c - Add attribute XVtable

Lscript.ld

Image_mover.c-UseL2 cache to lock code

4.FPGA代码量较大处理

如果FPGA代码比较大时需要做一个循环分块读FPGA代码再通过PCAP进行加载,不然会出现data abort的异常

5.移植到新的Vitis版本

Xilinx官方示例工程最新 的版本是基于SDK的2019.1,目前IDE已经升级到VITIS版本,下面介绍一下升级到最新Vitis版本的大概步骤:

a.新建一个fsbl application project

b.拷贝参考工程中的文件替换新建工程中文件,列表如下:

fsbl.h

fsbl_handoff.S

fsbl_hooks.c

fsbl_hooks.h

image_mover.c

image_mover.h

lscript.ld

main.c

pcap.c

pcap.h

qspi.c

qspi.h

translation_table.S

xil_exception.c

注:SDK和Vitis的bsp目录稍有不同,更新xil_exception.c的时候需要注意,

Vitis的目录在zynq_fsbl_bsp/ps7_cortexa9_0/libsrc/standalone_v7_2/src/下

6.打包BOOT.bin

使用bootgen工具进行打包,bif配置文件如下:

//arch = zynq; split = false; format = BIN

the_ROM_image:

{

[bootloader,xip_mode,offset = 0x1700]fsbl_xip.elf

[offset = 0x200000]system.bit

[offset = 0x700000]Application.elf

}

注:bootloader需要加上xip_mode的属性

如果您有DDRLESS方面问题,欢迎联系:

simonyang@comtech.com.cn

charlesxu@comtech.com.cn